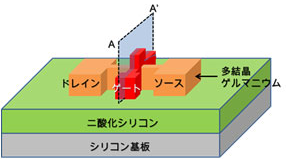

試作したゲルマニウムトランジスタの概念図(提供:産業技術総合研究所)

(独)産業技術総合研究所(産総研)は6月10日、3次元集積回路の実現に有望な多結晶ゲルマニウムトランジスタ技術を開発したと発表した。(株)富士通研究所、(株)東芝、(株)日立製作所、ルネサスエレクトロニクス(株)、(株)アルバックの5社と産総研の研究者らからなる連携研究体グリーン・ナノエレクトロニクスセンターの研究チームが取り組んだもので、集積回路の消費電力低減につながる成果という。

■新たな積層技術として期待

電子情報機器の消費電力を低減する方策の一つとして、集積回路の3次元積層化の開発が進んでいる。CMOS回路(論理回路)を立体的に積み重ね、上下の回路を電気的に接続して構成する。この電気的接続法には、基板を貫通して金属電極を形成するTSV技術や、微細なハンダや電極パッド同士を対向させて圧着するマイクロバンプがある。ただ、現状では配線ピッチが不十分だったり、コストが高かったりするなどの問題点がある。

研究チームは、配線を含む集積回路を連続的に多層に形成できる「積層CMOS技術」が有望と考え、多結晶ゲルマニウムトランジスタを用いる技術の開発に取り組んでいる。

多結晶ゲルマニウムは、下層のCMOS回路(論理回路)に影響のない低温で層間の絶縁膜上に形成できるという長所がある。また、電場をかけた時の電子・正孔の動きやすさを示す指標の「移動度」が大きいという特徴がある。移動度が大きいほど、低い電圧で必要な電流値を得ることができる。

今回、研究チームは多結晶ゲルマニウムを素材にフィン型と呼ばれる構造のトランジスタを試作した。フィン型は電流経路(チャネル)を垂直の板状(フィン)にしたもの。オン電圧時とオフ電圧時に流れる電流の比であるオン・オフ比を調べたところ、実用レベルに迫る5桁を超える値が得られたという。

この結果から、新技術はTSVやマイクロバンプなどを用いたチップ積層による3次元化技術を代替、あるいは補完する新たな3次元積層技術として期待できるとしている。